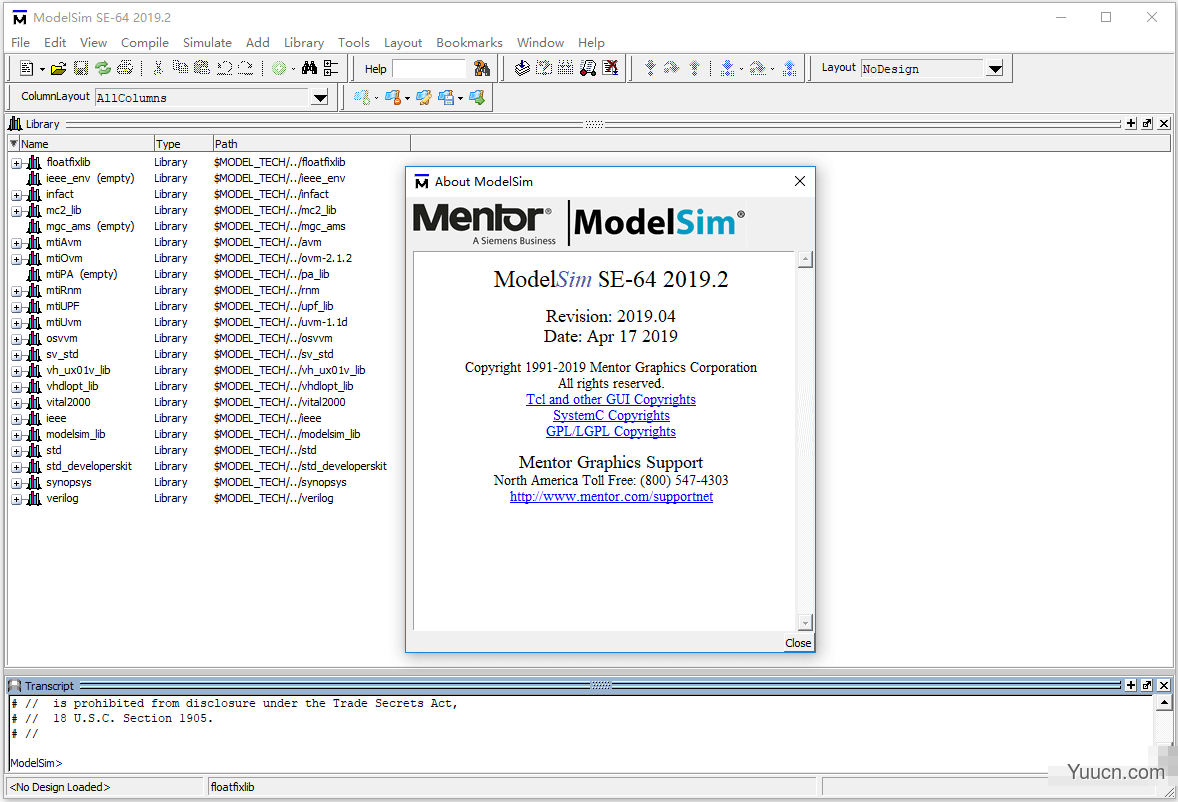

ModelSim SE-64 2019授权版是一款专业好用的HDL语言仿真软件,这个是ModelSim SE-64 2018的升级版本,拥有全新的性能,它为用户提供了易于使用,统一的调试和仿真环境,支持VHDL,Verilog,SystemVerilog等多种混合语言,燕且增加了新的功能,提升了相应的仿真速度,除此之外,还拥有自动更新活动的功能,比如Structure窗口中选择设计区域会自动更新Source,Signals,Process和Variables窗口。

ModelSim SE是ModelSim HDL(硬件描述语言)仿真软件的跨平台版本。 该软件被归类为软件套件的大块/系统仿真版本,而另外两个也属于仿真套件(ModelSim PE和ModelSim DE)的是块/仿真系统程序。 HDL环境使用户(通常是工程师)能够测试和调试HDL模型; 这是确保HDL模型设计通过验证的重要步骤。 它通常用于现场可编程门阵列(FPGA)电路设计和专用集成电路(ASIC)设计。

基础介绍

Mentor Graphics ModelSim SE是最流行的电子设计自动化模拟器和调试环境。 它具有良好的结构和清晰的设计,可以快速访问工作区。 ModelSim SE 2019主要用于电子设计自动化,用于开发和验证电子模块和系统,以便在现场可编程门阵列或集成电路上实现。 它是帮助设计人员处理VHDL,Verilog和SystemC的电子硬件和软件设计解决方案的最佳软件。 为了克服日益复杂的电路板和芯片设计领域的设计挑战,有vopt性能模式。

该软件的一般组件包括HDL编辑器,项目管理系统,源代码模板,编译数据库和本机编译架构,以及增量编译。 ModelSim SE支持VHSIC硬件描述语言(VHDL)和Verilog。借助vopt性能模式,工程师可以将Verilog和混合VHDL / Verilog RTL仿真性能提高多达10倍。 借助vopt模式,门级性能也可提高4倍,容量提高2倍以上。 它还支持非常快速的时间到下一次模拟周转,同时通过其新的黑盒使用模型(称为b-box)保持高性能。 b-box帮助设计人员编译不变元素并优化一次,并在运行测试平台的修改版本时重复使用。 在运行大量测试用例时,它可以提供高达3倍的显着改进。

ModelSim SE-64 2019安装授权教程

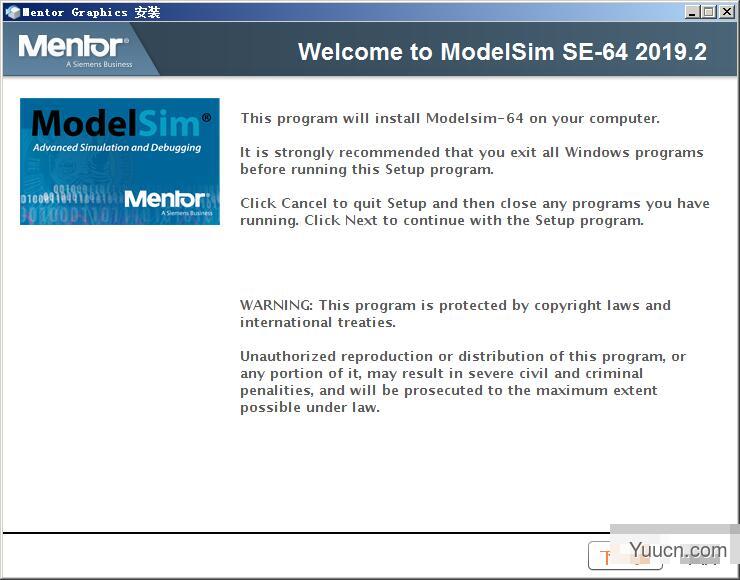

1、双击“modelsim-win64-2019.2-se.exe”开始解压安装包

2、加载完成后进入到ModelSim SE-64 2019的安装向导界面

3、继续下一步选择软件安装目录,默认为“C:\modeltech64_2019.2”

4、提示目录不存在是否创建,点击是

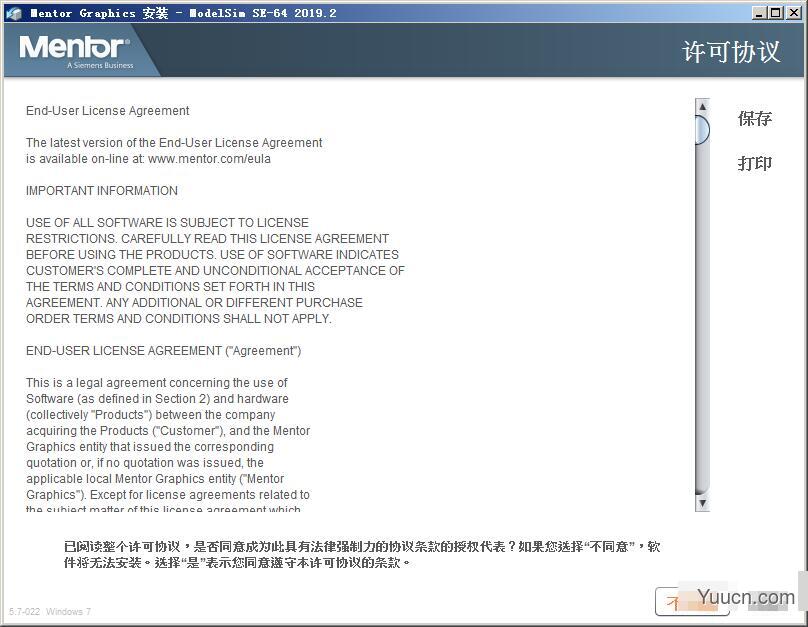

5、出现软件的许可协议,点击同意继续

6、然后就会开始ModelSim SE-64 2019的安装了

7、稍等一会儿就会完成软件的安装了

8、复制Crack所有文件到C:\modeltech64_2019.2\win64【默认路径】

运行patch64_dll.bat,将生成的许可证另存为LICENSE.TXT,保存一个指定位置

9、建系统环境变量:

变量名:LM_LICENSE_FILE

变量值:LICENSE.TXT的路径。

10、授权完成,Enjoy

软件功能

一、高级代码覆盖率

ModelSim的高级代码覆盖功能和易用性降低了利用这一宝贵验证资源的障碍。

ModelSim高级代码覆盖功能为系统验证提供了有价值的指标。所有覆盖信息都存储在统一覆盖数据库(UCDB)中,该数据库用于收集和管理高效数据库中的所有覆盖信息。可以使用分析代码覆盖率数据的覆盖实用程序,例如合并和测试排名。覆盖结果可以交互式查看,模拟后或多次模拟运行合并后查看。代码覆盖度量可以按实例或设计单位报告,从而提供管理覆盖数据的灵活性。

二、混合HDL仿真

ModelSim将仿真性能和容量与模拟多个模块和系统以及实现ASIC门级别签核所需的代码覆盖和调试功能相结合。全面支持Verilog,SystemVerilog for Design,VHDL和SystemC为单语言和多语言设计验证环境提供了坚实的基础。ModelSim易于使用且统一的调试和仿真环境为当今的FPGA设计人员提供了他们不断增长的高级功能以及使他们的工作高效的环境。

三、有效的调试环境

ModelSim调试环境为Verilog,VHDL和SystemC提供了广泛的直观功能,使其成为ASIC和FPGA设计的首选。

ModelSim通过智能设计的调试环境简化了发现设计缺陷的过程。ModelSim调试环境有效地显示设计数据,以便分析和调试所有语言。

ModelSim允许在保存结果的仿真后以及实时仿真运行期间使用许多调试和分析功能。例如,coverage查看器使用代码覆盖率结果分析和注释源代码,包括FSM状态和转换,语句,表达式,分支和切换覆盖率。

信号值可以在源窗口中注释并在波形查看器中查看,通过对象及其声明之间以及访问文件之间的超链接导航简化调试导航。

可以在列表和波形窗口中分析竞争条件,增量和事件活动。可以轻松定义用户定义的枚举值,以便更快地了解模拟结果。为了提高调试效率,ModelSim还具有图形和文本数据流功能。

ModelSim与Mentor的旗舰模拟器Questa共享一个共同的前端和用户界面。这样,如果客户需要更高的性能并支持高级验证功能,则可以轻松升级到Questa。

软件特色

1、统一的混合语言模拟引擎,易于使用和性能

2、支持的Verilog,SystemVerilog的设计,VHDL和SystemC对复杂的设计环境的有效核查

3、快速调试,易于使用,多语言调试环境

4、高级代码覆盖和分析 工具,可快速覆盖范围

5、交互式和后期模拟调试可用,因此两者都使用相同的调试环境

6、强大的波形 比较,便于分析差异和错误

7、统一覆盖数据库,具有完整的交互式和HTML报告和处理功能,可以在整个项目中理解和调试覆盖范

8、与HDL Designer和HDL Author相结合,可实现完整的设计创建,项目管理和可视化功能

评论(0)